DMA — Direct Memory Access, механизм, использующийся для непосредственного обмена данными между устройством и оперативной памятью компьютера, минуя центральный процессор.

Контроллер DMA — Используется для уменьшения нагрузки на центральный процессор в случае длительного обмена большим потоком данных с устройствами. К таким устройствам могут быть причислены:

- Жёсткие диски (IDE, ATA, SCSI ).

- Приводы для гибких магнитных накопителей ( CD , PCI Bus Master . ISA DMA — старый контроллер DMA, который описан ниже. В современные ПК устанавливаются два контроллера DMA:

- 8-битный (каналы 0, 1, 2, 3).

- 16-битный (каналы 4, 5, 6, 7).

В данном случае разрядность контроллера указывает режим передачи данных (8-битный, 16-битный).

Среди этих восьми каналов наиболее часто используются:

-

Канал 2 — для работы с гибкими дисками ( Порты [ ]

- CAR (Current Address Register) — регистр текущего адреса ячейки памяти, используемой в данный момент для выполнения операции обмена данными.

- CWR (Current Word Register) — регистр счётчика слов, подлежащих передаче минус один.

- PAR (Page Address Register) — регистр адреса страницы, служит для задания старших разрядов адресов (4 бита для DMA-1 и 8 бит для DMA-2).

- BAR (Base Address Register) — регистр базового адреса буфера (смещение), с которым осуществляется обмен данными. Служит для начальной загрузки значения в регистр CAR.

- BWCR (Base Word Count Register) — регистр базового числа циклов DMA (общее число передаваемых слов минус единица), служит для начальной загрузки значения в регистр CWR.

Фактически, регистр CAR имеет тот же адрес, что и BAR, а CWR — тот же, что BWCR. Отличие cостоит в том, что доступ к CAR и CWR осуществляется только при чтении данных из портов, а к BAR и BWCR — только при записи данных в порты.

Лекция «DMA. Кэш прямого отображения»

Весь список портов регистров DMA для каналов можно представить следующей таблицей:

Помимо этого, у каждого контроллера DMA есть свой набор регистров только для записи:

Управляющий регистр CR (Command Register) задаёт параметры работы контроллера DMA, общие для всех каналов микросхемы. Регистр представляет собой следующую структуру:

- бит 7 — уровень сигнала подтверждения DACK (1 — высокий, 0 — низкий).

- бит 6 — уровень сигнала подтверждения DREQ (1 — высокий, 0 — низкий).

- бит 5 — цикл записи (1 — расширенный, 0 — задержанный).

- бит 4 — приоритеты (1 — циклически меняются, 0 — фиксированы).

- бит 3 — сжатие цикла по времени.

- бит 2 — управление работой контроллера (1 — запрещена, 0 — разрешена).

- бит 1 — разрешение захвата канала 0 для режима память/память.

- бит 0 — режим работы (0 — обычный, 1 — память/память).

Регистр программного запроса RR (Request Register) имеет вид:

- биты 7-3 — не используются.

- бит 2 — запрос на DMA (0 — сбросить, 1 — установить).

- биты 1-0 — номер канала.

Регистр маскирования канала CMR (Channel Mask Register) позволяет временно блокировать сигнал запроса на обслуживание (DREQ) для определённого канала. Содержимое регистра представляется следующим образом:

Direct Memory Access — DMA — Simplified Explanation

- биты 7-3 — не используются (должны быть равны нулю).

- бит 2 — запрос на DMA (0 — сбросить, 1 — установить).

- биты 1-0 — номер канала.

Регистр установки режима работы MR (Mode Register) позволяет задать режим работы канала:

- биты 7-6 — режим обслуживания:

- 00 — передача по требованию.

- 01 — одиночная передача.

- 10 — блочная передача.

- 11 — каскадирование.

- 00 — тарификация.

- 01 — запись.

- 10 — чтение.

- 11 — запрещённая комбинация.

Регистр сброса триггера байтов предназначен для сброса переключателя младший/старший разряд для чтения или записи 16-битных значений из/в 8-битные порты 0x00-0x08. Очередной байт, переданный в эти порты, будет счиаться младшим, а следующий за ним — старшим.

Регистр сброса контроллера предназначен для сброса контроллера DMA, который осуществляется при записи любого значения в соответствующий ему порт.

Сброс регистра маски контроллера предназначен для снятия маскирующих битов со всех каналов одновременно. Операция осуществляется записью любого значения в этот регистр.

Регистр одновременной записи всех масок каналов WAMR (Writa All Mask Register) предназначен для одновременного изменения масок всех каналов контроллера. Регистр имеет вид:

- биты 7-4 — зарезервированы (0).

- бит 3 — маскирование канала 3.

- бит 2 — маскирование канала 2.

- бит 1 — маскирование канала 1.

- бит 0 — маскирование канала 0.

Регистр состояния SR (Status Register) имеет те же номера портов, что и регистр CR, но доступен только для чтения. Формат регистра следующий:

- бит 7 — обслуживание канала 3 разрешено.

- бит 6 — обслуживание канала 2 разрешено.

- бит 5 — обслуживание канала 1 разрешено.

- бит 4 — обслуживание канала 0 разрешено.

- бит 3 — конечный отсчёт по каналу 3 достигнут.

- бит 2 — конечный отсчёт по каналу 2 достигнут.

- бит 1 — конечный отсчёт по каналу 1 достигнут.

- бит 0 — конечный отсчёт по каналу 0 достигнут.

Функции [ ]

Пример маскирования канала DMA:

int DMAMasks; // В DMAMasks хранится информация о маскировании всех 8 каналов DMA void SetDMAMask(int channel) DMAMasks |= (1<channel); if (channel>=4) outportb(0xde, DMAMasks>>4); // используется WAMR DMA-2 else outportb(0x0f, DMAMasks // используется WAMR DMA-1 >

void ClearDMAMask(int channel) DMAMasks channel)); if (channel>=4) outportb(0xde, DMAMasks>>4); else outportb(0x0f, DMAMasks >

Сброс триггера байтов:

void ClearDMAByteTrigger(int channel) if (channel4) outportb(0x0c, 0xaa); // всё равно какое значение писать else outportb(0xd8, 0xaa); // всё равно какое значение писать >

Установка режима работы DMA:

void SetDMAWorkMode(int channel, int mode) int chan=channel // chan — номер канала, mode — режим if (chan4) outportb(0x0b, ((mode0x3))); else outportb(0xd6, ((mode0x3))); >

Пример записи адреса буфера для канала 2 контроллера DMA-1:

void SetDMABufferAddress_ch2(int address) // триггер байтов должен быть сброшен outportb(0x04, address); outportb(0x04, address>>8); outportb(0x81, address>>16); >

Пример установки счётчика слов для канала 2 контроллера DMA-1:

void SetDMACycles_ch2(int cycles) // триггер байтов должен быть сброшен int counter=cycles-1; outportb(0x05, counter); outportb(0x05, counter>>8); >

Пример инициализации канала DMA контроллера

// подготовка канала 2 к приёму данных от FDC SetDMAMask(2); // маскировать канал на время операций ClearDMAByteTrigger(2); // сбросить триггер байтов для канала 2 SetDMAWorkMode(2, 0x44); // установить режим работы — запись в буфер SetDMABufferAddress_ch2(0x20000); // буфер находится по физическому адресу 0x20000 SetDMACycles_ch2(512); // 512 = размер сектора диска ClearDMAMask(2); // размаскировать канал 2 // подача команды контроллеру на чтение сектора

Источник: osdev.fandom.com

Каналы прямого доступа к памяти (DMA)

Передача данных в режиме прямого доступа к памяти (Direct Memory Access, DMA) требуется при обмене данными между оперативной памятью и высокоскоростными устройствами. В режиме прямого доступа периферийное устройство связано с оперативной памятью непосредственно через каналы прямого доступа (каналы DMA), a не через внутренние регистры микропроцессора.

Наиболее эффективным такой режим обмена данными бывает в ситуациях, когда требуется высокая скорость для передачи большого объема информации (например, при загрузке данных в память с компакт-диска). Для инициализации процесса прямого доступа на системной шине используются соответствующие сигналы. Так, устройство, требующее прямой доступ к памяти, по одному из свободных каналов DMA обращается к контроллеру, сообщая ему путь (адрес), откуда или куда переслать данные, начальный адрес блока данных и объем данных (рис. 5.19). Инициализация обмена происходит с участием процессора, но собственно передача данных осуществляется уже под управлением контроллера DMA, а не процессора.

Из всех каналов DMA стандартно задействован только канал DMA 2 для обмена данными с дисководом гибких дисков. Каналы DMA 1 и DMA 2 обычно используются звуковыми картами. Один канал DMA может использоваться различными устройствами, но не одновременно, например, канал DMA 1 — для звуковой карты и стримера. Однако в этом случае вы не сможете одновременно слушать музыку и записывать данные на ленту.

Адреса портов ввода/вывода

В PC любое устройство (контроллеры, установленные на картах расширения или на материнской плате) за исключением оперативной памяти рассматривается центральным процессором как периферийное.

Обмен данными между CPU и периферийными устройствами осуществляется через так называемые порты ввода/вывода. Конструктивно порт ввода/вывода — это буферное устройство или регистр контроллера, процессора обработки сигналов и т. п., которые непосредственно подключены к шине ввода/вывода PC.

Для управления обменом данными между аппаратными компонентами компьютера каждому порту ввода/вывода присваивается свой уникальный шестнадцатеричный номер (адрес порта), например 2F8h, 370h. Можно провести аналогию с почтой: чтобы письмо попало по назначению, на конверте должен быть правильно указан адрес получателя. Напомним — символ «h» (hex) означает, что адрес указывается в шестнадцатеричной системе исчисления.

В IBM-совместимых PC можно адресовать (использовать) 65 536 (216) портов ввода/вывода (хотя большинство из них, как правило, не используется). Причем адресное пространство портов ввода/вывода не совпадает с адресным пространством памяти, что дает возможность иметь полный объем памяти и полный набор портов ввода/вывода. Стандартный диапазон адресов портов ввода/вывода для IBM PC-совместимых компьютеров составляет О-3FFH включительно, хотя реально можно использовать адреса вплоть до FFFFh (например, порты процессора WT-синтеза звуковой карты (см. главу 14) имеют адреса в диапазоне 620h-E23h). Сюда входят порты контроллеров клавиатуры, жестких и гибких дисков, видеоадаптеров EGA/VGA, звуковых карт, последовательных и параллельных интерфейсов, игровых портов и любого другого периферийного оборудования.

Естественно, адресация портов осуществляется центральным процессором при выполнении той или иной программы. Для того чтобы исключить необходимость указания конкретного адреса каждого порта ввода/вывода при программировании, а также для оперативного их изменения в зависимости от конкретной конфигурации компьютера, существует понятие базовый адрес порта ввода/вывода (Base Address Input/Output).

Задача

(олифер, стр 189) В unix для адресации используется метод перечисления номеров кластеров. В данном случае i-узел выглядит следующим образом: в нем 10+3+2+1=16 полей по 4 байта.

Каждый узел косвенной адресации содержит (размер блока/размер адреса) (2кб/4б) 512 полей

Общее кол-во полей i-узла = 10+3*512+2*512*512+4*512*512*512= 537396746 полей – столько блоков может включать файл. Его объем = объем блока * число блоков~= 1Тб. С другой стороны, размер файла может быт ограничен максимальным числом кластеров которое можно адресовать. Если размер адреса = 4кб, то можно адресовать 2^4096 блоков. В нашем случае это число значительно больше чем полей, т.е это ограничением максимального размера файла не является.

Понравилась статья? Добавь ее в закладку (CTRL+D) и не забудь поделиться с друзьями:

Источник: studopedia.ru

Термин: Прямой доступ к памяти (DMA)

Термин прямой доступ к памяти (ПДП, DMA — Direct Memory Access) возник на заре развития процессорной техники. Этот термин фактически означает прямой доступ к памяти со стороны периферийного устройства без участия процессора. Смысл такого доступа очевиден: освободить процессор от рутинных операций пересылки данных между внешним устройством и памятью, а также из памяти в память, и за счёт этого сэкономить ресурс процессора (процессорное время), чтобы повысить его производительность на операциях обработки данных.

То устройство (функциональный узел), которое управляет пересылкой данных, называется контроллером ПДП. По мере развития процессорной техники, контроллеры ПДП стали многоканальными, что позволило поддерживать несколько каналов доступа к памяти от разных периферийных устройств, а также и из памяти в память. Сами архитектуры процессорных систем сильно видоизменялись, контроллеры ПДП, периферия и память входили в разные части процессорных систем, но общая идея прямого доступа к памяти фактически не изменилась. Упомянем далее несколько конкретных реализаций DMA.

У сигнальных процессоров ADSP-2185M есть два варианта доступа к внутренней памяти процессора со стороны внешнего устройства: IDMA и BDMA. Сигнальные процессоры Blackfin ADSP-BF523 имеют канал доступа Host DMA к памяти процессора со стороны внешнего устройства.

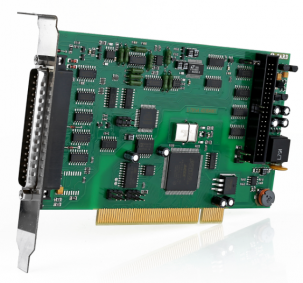

Режим DMA поддерживается на интерфейсах компьютера: ISA, PCI, PCI Express. Но для осуществления пересылок по DMA необходимо, чтобы периферийное устройство (вставленная в слот плата) поддерживала DMA.

Остановимся отдельно на режиме BUS Master компьютерных интерфейсов PCI и PCI Express. Плата, вставленная в слот, поддерживающая режим BUS Master, способна сама на время захватить шину, полностью взяв на себя роль контроллера ПДП. Для пользователя ПК это означает, что процессор во время пересылки данных по DMA (из платы в память ПК и обратно) может заниматься другими важными задачами, в том числе, и задачами пользователя.

Важно сказать, что отсутствие поддержки DMA, например, со стороны используемого PCI-устройства для системного интегратора должно означать, что для сохранения свойства воспроизводимости (унификации, переносимости) системы на другие компьютеры, нельзя закладываться на максимальные скорости передачи данных PCI-устройства, заявленные производителем, поскольку, в каждом конкретном случае максимальная скорость будет сильно зависеть не только от самого PCI-устройства, но и от текущей загрузки процессора компьютера, особенностей программной среды и чипсета материнской платы, от ситуации, когда не-DMA обращения к PCI-устройству на низком уровне системы будут не одинаково эффективно реализованы на фоне групповых пересылок, что может привести к зависимости от типа материнской платы, от операционной системы.

| Перейти к другим терминам | Cтатья создана: | 14.08.2014 |

| О разделе «Терминология» | Последняя редакция: | 25.08.2019 |

Пример использования термина

Термин используется при описании архитектур различных систем сбора данных, например, в документации перечисленных ниже систем.

АЦП: 16 бит; 16/32 каналов;

±0,2 В…10 В; 2 МГц

ЦАП: 16 бит; 2 канала; ±5 В; 1 МГц

Цифровые входы/выходы:

18/16 TTL 5 В

Интерфейс: PCI Express

Плата АЦП/ЦАП

16/32 каналов, 16 бит, 2 МГц, PCI Express

L-502

АЦП: 16 бит; 16/32 каналов;

±0,2 В…10 В; 2 МГц

ЦАП: 16 бит; 2 канала; ±5 В; 1 МГц

Цифровые входы/выходы:

17/16, ТТЛ 5 В

Интерфейс: USB 2.0 (high-speed), Ethernet (100 Мбит)

Гальваническая развязка.

Модуль АЦП/ЦАП

16/32 каналов, 16 бит, 2 МГц, USB, Ethernet

E-502

АЦП: 14 бит; 16/32 каналов;

±0,07 В…10 В; 400 кГц

ЦАП: 12 бит; 2 канала; ±5 В; 8 мкс

Цифровые входы/выходы:

16/16 TTL 5 В

Интерфейс: PCI

Плата АЦП/ЦАП

16/32 каналов, 14 бит, 400 кГц, PCI

L-791

АЦП: 14 бит; 16/32 каналов;

±0,156 В…10 В; 400 кГц

ЦАП: 12 бит; 2 канала; ±5 В; 8 мкс

Цифровые входы/выходы:

16/16 TTL 5 В

Интерфейс: USB 2.0

Модуль АЦП/ЦАП

16/32 каналов, 14 бит, 400 кГц, USB

Источник: www.lcard.ru